# Interrupts, Buses

Chapter 6.2.5, 8.2-8.3

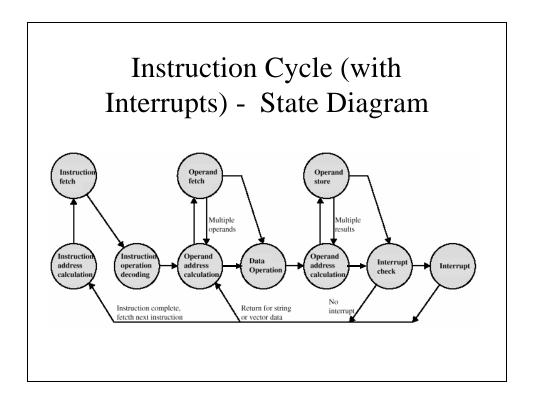

### Introduction to Interrupts

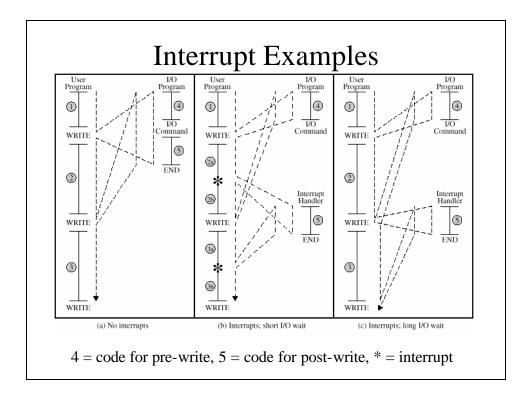

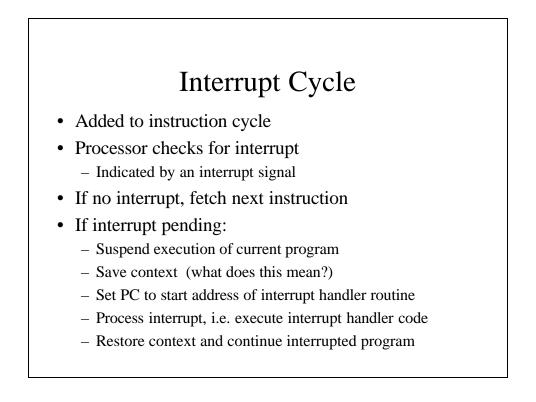

- Interrupts are a mechanism by which other modules (e.g. I/O) may interrupt normal sequence of processing

- Four general classes of interrupts

- Terms: Traps when initiated by system, Interrupt when initiated by programmer

- Program e.g. overflow, division by zero

- Timer, internal timer, used in pre-emptive multi-tasking

- I/O from I/O controller

- Hardware failure, e.g. memory parity error

- Particularly useful when one module is much slower than another, e.g. disk access (milliseconds) vs. CPU (microseconds or faster)

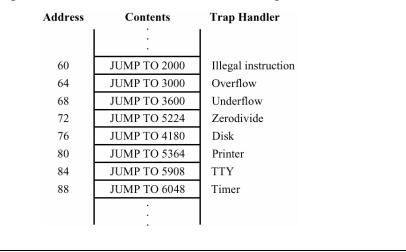

# Branch Table for Handlers

How do we know where to go to execute the interrupt handler? Lookup in a branch table, also called the interrupt vector

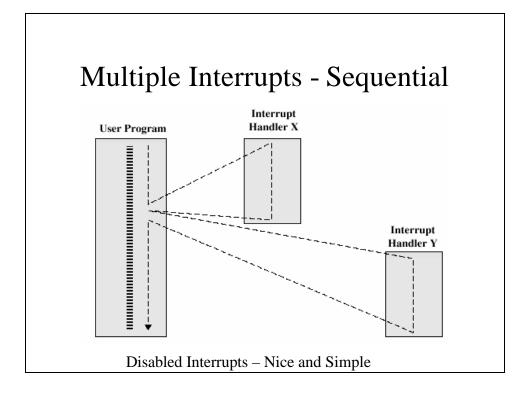

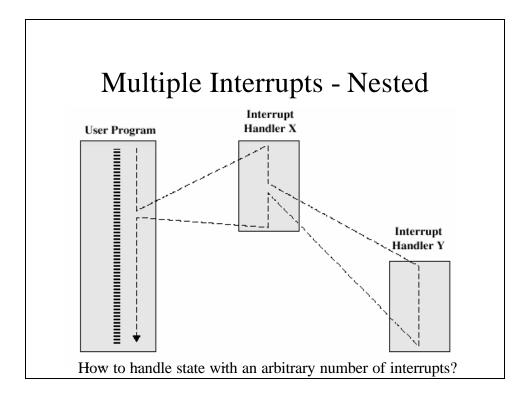

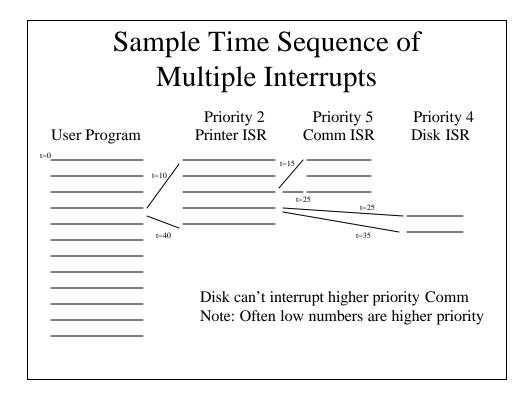

# Multiple Interrupts

- Disable interrupts Sequential Processing

- Processor will ignore further interrupts whilst processing one interrupt

- Interrupts remain pending and are checked after first interrupt has been processed

- Interrupts handled in sequence as they occur

- Define priorities Nested Processing

- Low priority interrupts can be interrupted by higher priority interrupts

- When higher priority interrupt has been processed, processor returns to previous interrupt

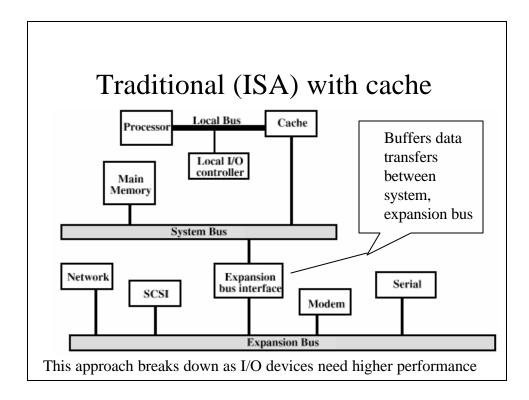

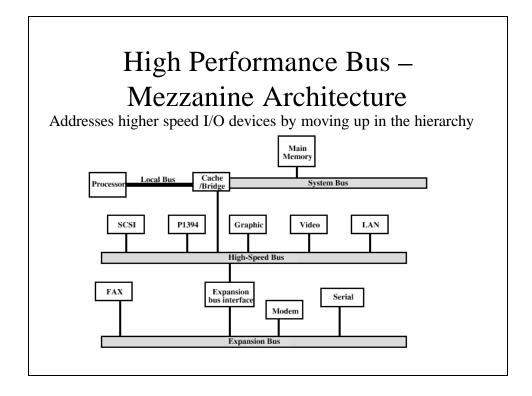

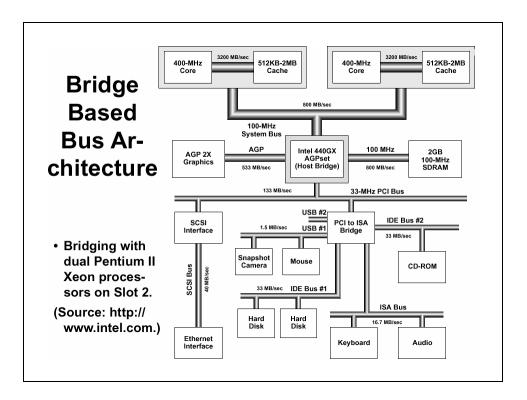

## Buses

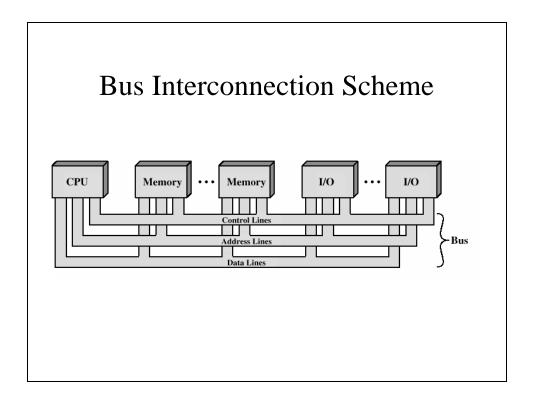

- There are a number of possible interconnection systems. The most common structure is the **bus**

- Single and multiple BUS structures are most common

- e.g. Control/Address/Data bus (PC)

### What is a Bus?

- A communication pathway connecting two or more devices

- Usually broadcast

- Everyone listens, must share the medium

- Master can read/write exclusively, only one master

- Slave everyone else. Can monitor data but not produce

- Often grouped

- A number of channels in one bus

- e.g. 32 bit data bus is 32 separate single bit channels

- Power lines may not be shown

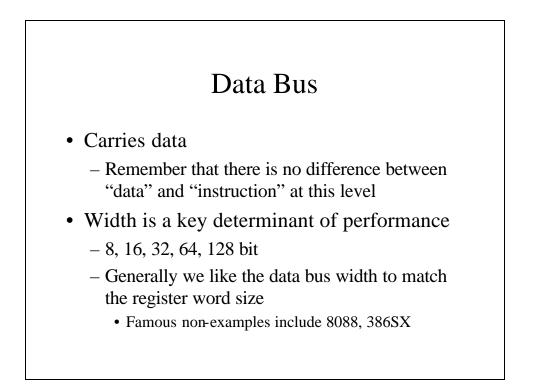

- Three major buses: data, address, control

## Address bus

- Identify the source or destination of data

- In general, the address specifies a specific memory address or a specific I/O port

- e.g. CPU needs to read an instruction (data) from a given location in memory

- Bus width determines maximum memory capacity of system

- 8086 has 20 bit address bus but 16 bit word size for 64k directly addressable address space

- But it could address up to 1MB using a segmented memory model

| Control Bus                                         |                                                                                                                                  |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| • Control and timing info                           | ormation                                                                                                                         |

| <ul> <li>Determines what modul<br/>lines</li> </ul> | les can use the data and address                                                                                                 |

| might be a request for a                            | nd data, it must (1) obtain<br>us, and (2) transfer data – which<br>nother module to send data<br>ution for control is performed |

| <ul> <li>Typical control lines</li> </ul>           |                                                                                                                                  |

| <ul> <li>Memory read</li> </ul>                     | - Memory write                                                                                                                   |

| – I/O read                                          | - I/O write                                                                                                                      |

| <ul> <li>Interrupt request</li> </ul>               | - Interrupt ACK                                                                                                                  |

| Due Dequest                                         | - Bus Grant                                                                                                                      |

| <ul> <li>Bus Request</li> </ul>                     |                                                                                                                                  |

## Big and Yellow?

- What do buses look like?

- Parallel lines on circuit boards

- Ribbon cables

- Strip connectors on mother boards

- e.g. PCI

- Sets of wires

- Limited by physical proximity time delays, fan out, attenuation are all factors for long buses